2023.10.14 - [해외주식/Synopsys] - Synopsys 기업 소개

Synopsys 기업 소개

투자를 하면서 정리한 개별 기업 정보를 하나씩 써보려 한다. 먼저 기업 설명 및 분석을 진행한 후, 사업별 추가 분석, Risk, Valuation 등의 구성으로 진행할 예정이며, 내 전공 분야와 밀접한 관련

stockvaluation.tistory.com

2. 사업 별 분석

전공적인 내용보다는 new player의 시장 진입 난이도 (= 경제적 해자), market share, 시장의 성장성에 초점을 두고 내용을 작성하였다. EDA의 경우에만 전반적인 칩 제작 과정을 설명하는 것이 좋을 것 같아 조금 더 자세히 설명하였다.

2.1 EDA (Electronic Design Automation)

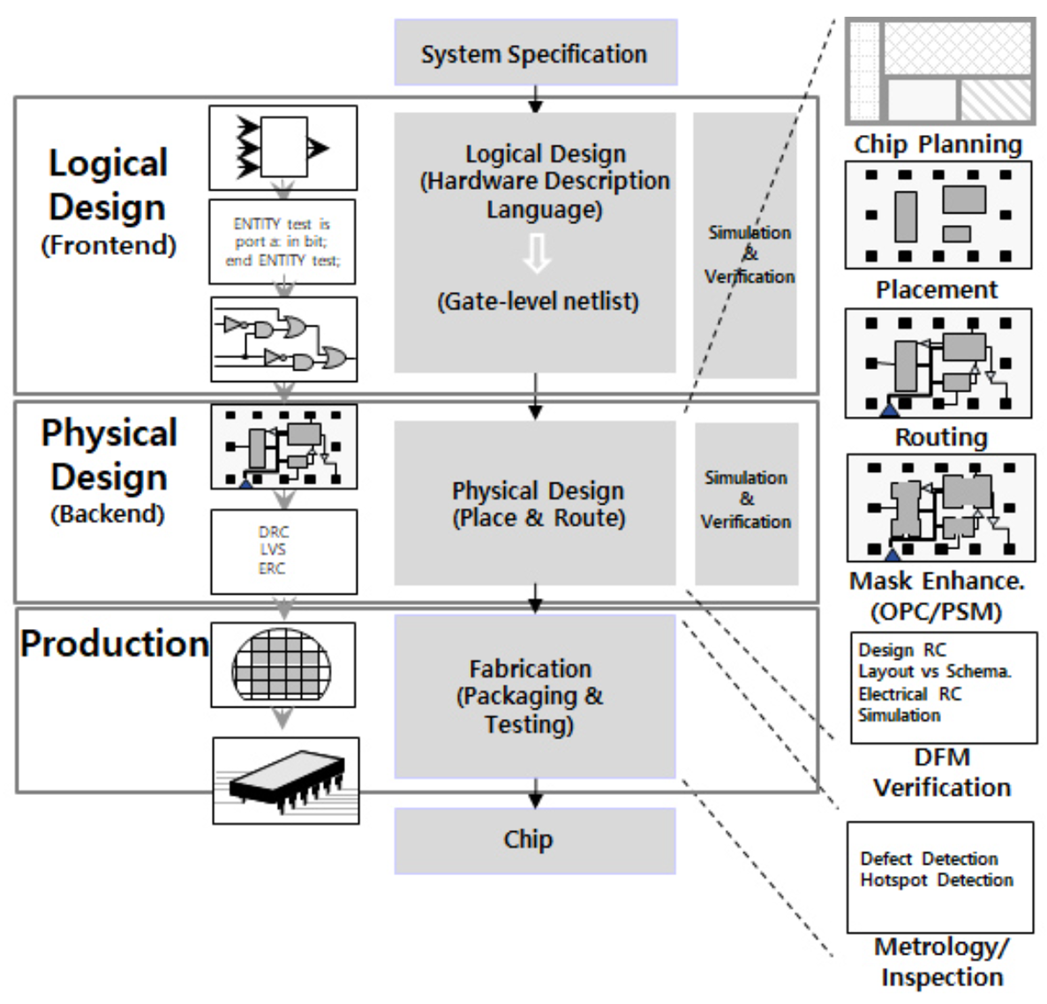

EDA는 반도체 설계에서 사용하는 tool들을 의미한다. Transistor level의 소자 설계부터 (이쪽은 사람이 손으로 하는 것도 매우 많다) digital level에서의 P&R, 그리고 photo 및 양산까지, 반도체 설계의 모든 단계에서 사용된다고 보면 된다. 아직 analog circuit 설계의 경우는 사람이 하는 경우가 많지만 이 또한 결국에는 automation이 적용될 것으로 생각한다.

반도체 설계 과정은 아래 그림과 같이 크게 Logical design (frontend)와 Physical design (backend)로 나뉠 수 있다.

간략하게 설명하면, 먼저 logic design에서는 구현하고자 하는 기능을 Verilog 등의 언어를 활용하여 RTL 코딩을 한다. RTL code는 Netlist라는 소자 (gate) 간의 연결 관계를 표현하는 schematic (회로도)으로 변환되고, 검증된다. 보통 각 IP 단위로 먼저 검증이 된다.

이후, physical design 단계에서는 각각의 IP (= Macro)를 집적하기 위해 각 macro들을 겹치지 않도록 잘 Floorplan 한다. Floorplan의 목적은 P&R (Place and Route) 전 설계의 방향을 잡아놓는 것으로 보면 되는데, standard cell들을 배치하기 전 IP들을 미리 잘 배치하는 것으로 생각하면 된다.

Floorplan 후 IP 및 standard cell들을 배치 (Placement) 하고 각 IP 간의 input/output 역할을 하는 pin들을 연결한다 (Routing). Physical design의 결과물은 GDS 라는 파일 형태로 저장된다.

GDS 파일을 사용하여 DRC (Design Rule Check), LVS (Layout vs Schematic) 등의 검증 과정을 거친 후, 실제 생산을 위한 단계를 거친다.

GDS 파일의 도면이 의미하는 것은 결국 wafer 표면에 형성되어야 하는 pattern이다. 이러한 pattern이 잘 합성되도록 OPC (Optical Proximity Correction) 등의 기법을 적용하는 것도 EDA의 역할이다.

마지막으로, MTO (mask tape out) 후 양산에 들어가게 되는데, 양산 과정에서도 수율 확보를 위해 MI (Metrology & Inspection) 등을 수행한다. 이렇게 반도체 설계 과정의 모든 부분에서 EDA가 사용된다고 보면 된다.

공정이 달라지고 미세화되면, 그에 따라 EDA tool에서 제공하는 기능도 더 발전한다. 예를 들어 최근 trend라고 볼 수 있는 Advanced packaging, Chiplet 등으로 패키지 관련 기술이 칩 기술과 연계되어야 하기에, 이를 위한 EDA 신기능이 필요하다.

또한, 공정이 미세화 됨에 따라 저항이 증가하는데, 이로 인해 IR Drop (전압 강하) 현상이 발생해 각 cell에 충분한 전압이 도달하지 못하게 된다. 이 문제는 10nm 이후 한자릿수 공정으로 진입하면서 수면 위로 떠올랐는데, 이는 칩의 성능을 낮추고, 심지어는 도중에 동작을 멈추게 되는 원인이 될 수 있기에 이를 고려한 설계가 필요하다.

EDA Market Share 및 성장성

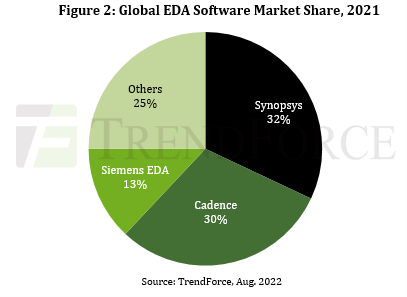

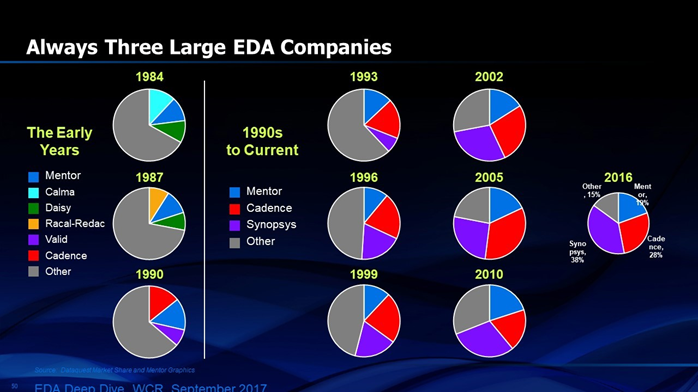

EDA market은 지난 포스트에서도 간략하게 설명하였지만, 아래와 같이 Synopsys, Cadence 가 절반 이상을 차지하고, 나머지 중에는 Siemens (Mentor), Ansys 정도가 10% 초반 대의 점유율을 가지는 과점 형태의 시장이다. 역사적으로 초기에는 다양한 업체가 있었지만, 기술력에서의 우위 등으로 현재의 시장 형태가 굳혀지게 되었다.

혁신적인 기술을 기반으로 하는 신생 업체가 나오는 경우도 있지만, 어차피 EDA 시장에서 고객사들은 신규 제품의 사용을 꺼려하기 때문에 EDA 빅3 업체가 해당 업체들을 인수하여 자사 제품에 반영하는 식으로 market이 형성되어 있다.

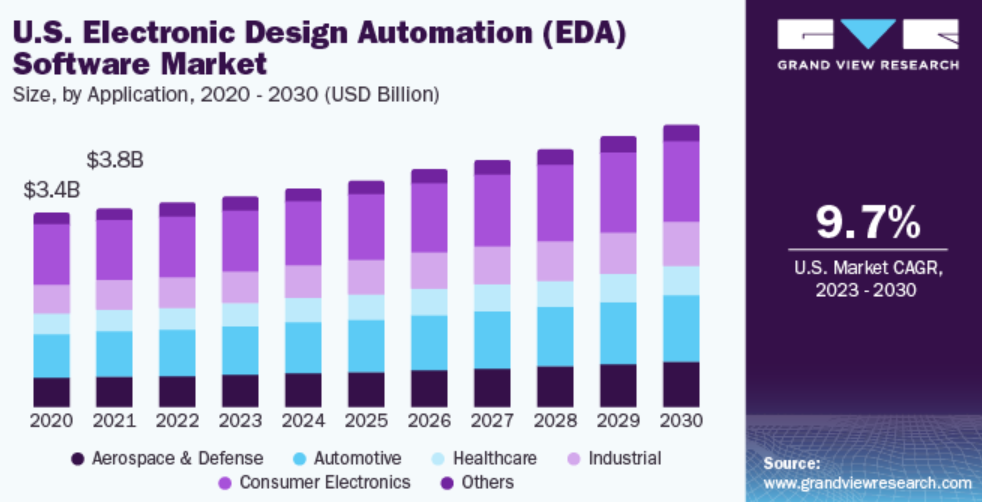

EDA market의 성장성은 연 9.7%로 예상되며, 전세계 기준으로는 (아래 그림은 US 기준) 2027년에 23조원 규모에 이를 것으로 생각된다.

또한 최근 AI의 발전으로, 이를 효율적으로 처리하기 위해 마이크로소프트, 아마존, 구글 (특히 TPU) 등 빅테크에서도 자체 칩을 만드려는 시도가 있어 칩 설계 시장의 성장성은 보장되어 있고, 이에 따른 EDA 시장의 성장성 또한 높을 것으로 예상된다.

2.2 IP

반도체에서의 IP는 누군가 이미 개발해놓은 design이라고 생각하면 된다. IP를 사용하는 이유는 공정이 미세화 됨에 따라 설계 및 검증에 들어가는 비용, 시간이 증가하기에, 기 검증된 제품인 IP의 사용이 더 효과적이기 때문이다. IP는 크게 Hard IP와 Soft IP로 나뉜다.

- Hard IP : IP 내부 구조 (RTL로 짜여진)을 변경할 수 없고, layout까지 이미 다 고정된 IP

- Soft IP : IP 내부 구조를 변경할 수 있어 layout 등을 재설정할 수 있는 IP

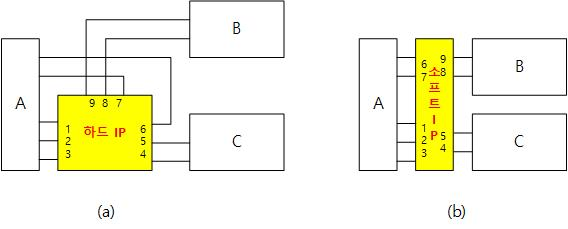

아래는 Hard IP와 Soft IP의 차이를 개략적으로 보여주는 그림으로, hard IP의 경우 layout이 고정되어 있어 routing이 soft IP에 비해 비효율적일 수 있는 것을 보여준다. 대신 soft IP는 새로 합성하고, layout 까지 진행해야 한다는 단점이 있다.

IP Market Share 및 성장성

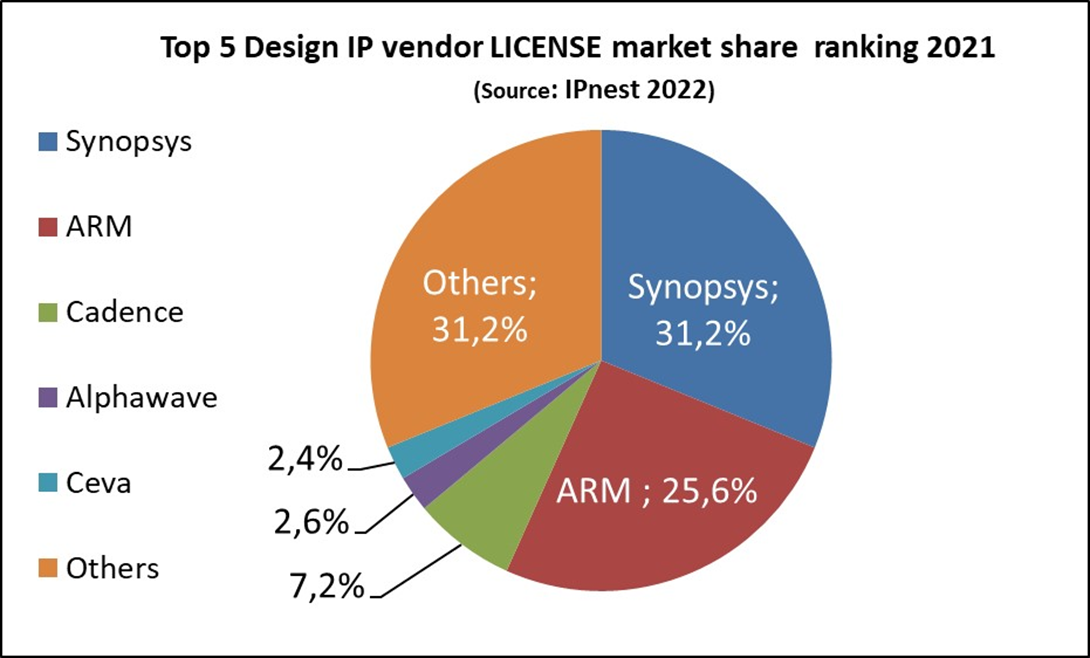

IP 시장의 market share는 아래와 같으며, Synopsys는 전체 IP 시장의 30% 정도를 점유하고 있다. 시놉시스의 모든 IP portfolio는 https://www.synopsys.com/dw/doc.php/ds/o/product_overview.pdf 에서 확인할 수 있다.

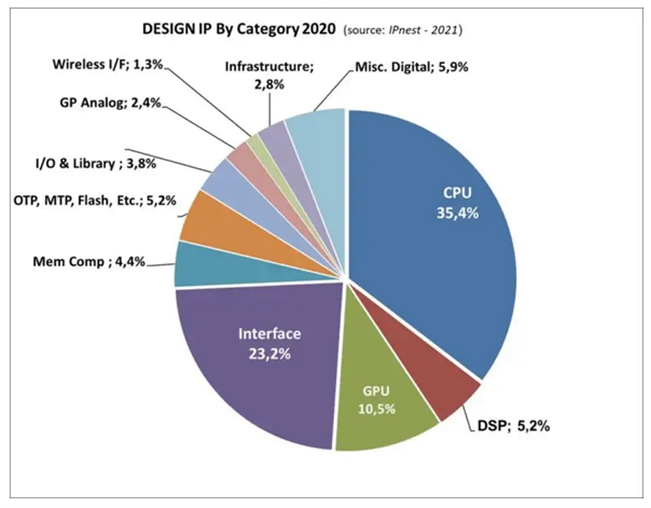

특히 시놉시스가 특히 강점을 보이는 분야는 Interface IP로, Interface IP 부분의 경우 Die-to-Die, PCIe, Ethernet, CXL, USB 등 대부분의 분야에서 다양한 공정 별 IP를 확보하고 있다.

칩 하나로 달성할 수 있는 성능이 점차 둔화됨에 따라, 반도체 trend가 여러 chip들을 연결하여 사용하는 것이기에 Interface IP 시장의 성장성은 전체 IP 시장에 비해 높은 편이다. 실제로, 2020년 기준 interface IP는 전체 IP 시장의 23%를 차지하고 있지만, 16, 17, 18년도에는 각각 16, 18, 20% 뿐을 차지하고 있었다.

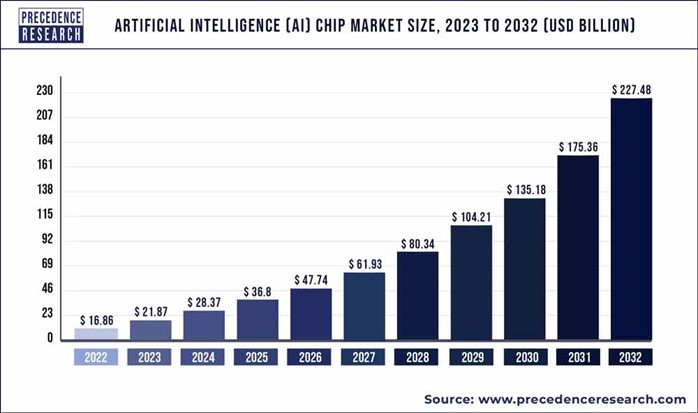

이러한 interface IP의 성장은 결국 AI 칩 성장의 발전과 함께 할 것으로 생각된다. AI chip market은 cagr 29.7%로 성장할 것으로 추정되고 있는데, 상술하였듯 단일 core로 성능을 뽑아내는 것에는 한계가 있기에 AI chip에 필수적인 것이 interface IP 이다. 이를 고려하면, interface IP 단일 시장도 10% 후반~20% 초반대의 성장률을 보일 것으로 생각된다.

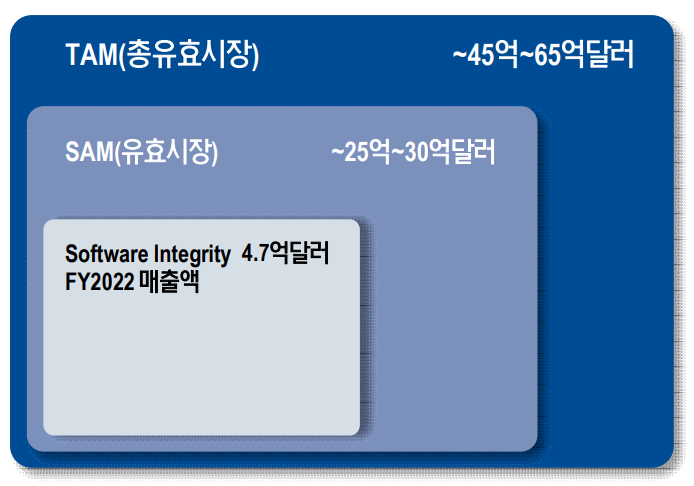

2.3 Software Integrity

이쪽 분야는 전공 분야는 아니기도 하고, 아무래도 워낙 분야 자체가 파편화 되어 있는 듯하여 자료를 찾기가 어려웠다. 10k 보고서에 따르면, 동사의 Software Integrity tool 종류는 크게 SW defect을 찾아내는 tool, SW security tool, DevOps testing pipeline (CI 등)의 구성을 도와주는 tool 로 구성되어 있다. 참고로 필자의 경우 이중 Coverity라는 정적분석 tool을 사용하고 있다.

SI 쪽은 워낙 많은 회사가 있기에, SI Market Share 도표는 첨부하지 않았다. SI 사업은 경쟁이 치열하지만, 시놉시스는 해당 분야에서 나름 알짜 회사들을 잘 M&A를 잘해왔고, 아직 시장 점유율도 높지 않아 성장성이 높기에 앞으로 한축을 담당할 수 있을 것으로 생각한다.

3. 투자 Risk

모든 기업의 제일 큰 투자 risk는 모종의 이유로 경제적 해자가 붕괴하는 상황일 것 이다. Synopsys 매출의 절반 이상이 EDA 관련 매출이기에 이에 대해 집중적으로 분석하였다.

먼저 AI 기반의 신기술로 EDA 시장에서 시놉시스의 점유율이 낮아질 수 있는 우려에 대해서는, 가능성이 거의 없다고 생각한다. 예를 들어 여러 EDA 분야 중 chip placement의 경우 구글에서 논문을 발표한 적이 있지만 (Chip Placement with Deep Reinforcement Learning, Chip Design with Deep Reinforcement Learning – Google Research Blog), Synopsys도 동일한 연구를 하고 있고, 이미 2020년에 DSO.ai (Design Space Optimization AI) 라는 reinforcement learning 기반의 툴을 출시하였다.

또한, 어차피 최근의 deep learning은 아키텍처보다도 결국 많은 데이터를 사용하여 learning하는 것이 성능을 향상시키기 제일 좋은 방법이라는 의견이 대세인데, 이미 EDA 시장을 과점하고 있는 동사와 Cadence (+ 지멘스, Ansys 정도) 외에는 data를 얻을 방법도 딱히 없을 것으로 생각된다.

이외에 Empyrean과 같은 중국 업체 등에서 EDA 기술 개발을 시도하고 있지만 전공자 입장에서는 상당히 부정적이다. 분야 특성상 이미 쌓아 놓은 기술력을 따라잡기도 어렵고, 특히, 공정이 미세화 될수록 필요한 연구도 많아지는데, 현재 중국 업체들의 현금 흐름으로는 정부 지원이 있다 하더라도 R&D에 그만큼 돈을 쏟기 어려울 것이다. 애초에 현재는 미-중 갈등으로 최신 공정에 대해서는 할 수도 없는 상황이기도 하다.

마지막으로, 고객 입장에서는 EDA 소프트웨어를 바꾸기가 쉽지 않다. 반도체의 개발은 완전히 새로운 디자인이 나오는 것이 아니라, 기존 디자인에서 계속 조금씩 수정하고, 이를 공정에 맞춰 변형하는 과정이기 때문이다. 즉 기존 결과들에 대해 축적된 data들이 중요하기에, 고객사 입장에서는 새로운 EDA 공급사를 선정하기 꺼려하고, 실무 엔지니어 입장에서도 새 tool을 사용하기 꺼려한다.

또한, 시놉시스, 케이던스의 tool을 학부 및 대학원 때부터 많이 이용하기에 해당 tool들을 계속 사용하는 것이 신입 사원의 교육 면에서도 이득이 있다. 필자는 computer architecture로 학위를 받았는데, 학부 및 대학원 때 두 회사의 tool 위주로 보았으며, 회사에서도 두 회사의 tool 사용율이 비슷하다. 특히, HW engineer들의 경우 SW engineer 들에 비해 익숙해진 tool 및 언어 (verilog 등) 외 새로운 것을 배우기 꺼리는 (그리고 힘들어하는) 경향이 있다.

IP 시장의 경우, EDA에 비해서는 경쟁자도 많고 해자도 더 낮지만, 여전히 충분히 우위를 가지고 있다고 생각한다.

예를 들어 위의 IP market share에 표시되어 있는 Alphawave의 경우, high speed serdes, 즉 interface IP 부분에서 강점을 보이고 있다. 그러나 IP 하나가 가지는 영향은 제한적이고, 시놉시스나 ARM과 같이 다수의 IP를 보유하고 있는 회사는 IP 판매 시 유지 보수가 빠르고 더 싼 가격에 제공할 수 있다는 강점을 가진다.

마지막으로 Software Integrity 시장의 경우, EDA 및 IP 시장에 비해서는 경쟁자도 더 많고, 그에 따라 해자도 더 낮다고 생각한다. 그러나, 시놉시스 매출 중 차지하는 비중은 낮기에 시놉시스 투자 시 큰 문제가 되지는 않을 것으로 생각한다.

'해외주식 > Synopsys' 카테고리의 다른 글

| Synopsys의 Ansys 인수 완료 (0) | 2024.01.18 |

|---|---|

| Synopsys의 Ansys 인수 시도 (0) | 2023.12.25 |

| 시놉시스 Synopsys 기업 분석 및 주가 전망 (2) (1) | 2023.10.30 |

| 시놉시스 Synopsys 기업 분석 및 주가 전망 (1) | 2023.10.21 |

| Synopsys 기업 소개 (1) | 2023.10.14 |